PLD (SVF, STAPL, ISC IEEE 1532)

Company Information:

Name: |

PLD (SVF, STAPL, ISC IEEE 1532) |

Category: |

|

Offered by: |

|

PLD (SVF, STAPL, ISC IEEE 1532) Description:

Almost all today's programmable logic devices (CPLDs and FPGAs) now utilise the IEEE std 1149.1 interface port to access their proprietary configuration circuits. Until 2001 the popular SVF (Serial Vector Format) was considered the de facto standard for streaming data into these parts and SVF remains popular to this day.

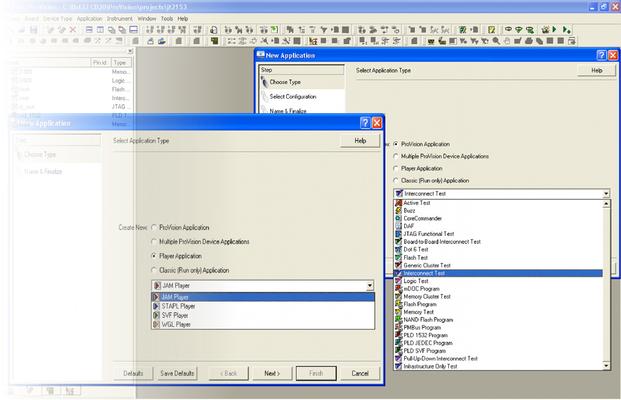

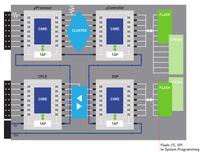

However as the IC vendors vied to produce the optimum data format/language for programming devices 'in-system' other standards appeared (JAM, STAPL, XSVF etc..) until the IEEE standards committee approved a universal standard that could be applied across designs bearing multiple vendor devices. The IEEE Std 1532 was finally approved in 2001 and as part of that standard a universal data format 'ISC' was introduced alongside enhanced BSDL models for compliant programmable parts.

Since the very first PLDs with JTAG programming were introduced JTAG Technologies have developed timely support packages that allow manufacturers to program all vendor parts at high speed. Today that support is provided through JTAG ProVision and the PIP and Symphony tester integration packages.

- Universal support for all CPLD and FPGA vendors

- Processes SVF, JAM/STAPL, ISC and JEDEC files

- Popularly used with Altera, Actel, Lattice, Xilinx etc..

Applications:

Device in-system program is a key application for JTAG/boundary-scan technology. Use as an add-on to structural testing at the ICT stage or as a precursor to functional testing. In-system programming helps greatly with configuration control and system firmware updates.

Benefits:

- Helps to reduce inventory of pre-programmed parts

- Allows unified system for both testing and device programming/configuration

- Provides link between structural and functional testing

- Can be utilised se to program test IP cores

Features:

- Supports JAM and STAPL (JESD71) formats

- Supports SVF through verbatim 'player' program and also as compiled JPF format files

- Handles Scan path interfaces devices such as Bridges and Gateways

- Allows current programming when targetting IEEE 1532 compliant devices

- Includes legacy JEDEC support fro older Lattice and Xilinx parts

PLD (SVF, STAPL, ISC IEEE 1532) was added in Jul 2015

PLD (SVF, STAPL, ISC IEEE 1532) has been viewed 745 times

19 More Products from JTAG Technologies B. V. :