#### **Preface**

Lin Chao

Editor

Intel Technology Journal

This Q3'98 issue of the *Intel Technology Journal (ITJ)* marks our first anniversary of publishing the *ITJ* on the Internet. From your questions and feedback so far, we know that the *ITJ* is being read all over the globe. Thank you for all your feedback and questions. Please keep them coming.

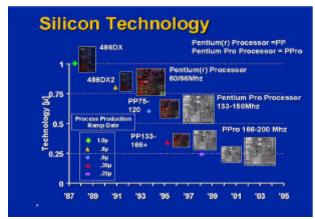

This Q3'98 issue describes one of Intel's most important technologies: our semiconductor process technology, the prize of Intel's technology jewels. The magic of silicon is basically that in every generation the dimension gets smaller, and processors get smaller, faster, and cheaper to build. This issue of the *ITJ* describes the challenges inherent in making this silicon magic happen.

The first two papers describe our 0.25 micron process technology used to manufacture the Intel® Celeron<sup>TM</sup> and Pentium® II processors. The 0.25 micron refers to the line-width dimensions etched into the silicon wafers. To illustrate how small 0.25 microns actually is, think about the fact that a typical pollen microspore measures between 10 and 100 microns. Using the 0.25 micron process technology, you could place between 40 and 400 transistors in the width of a pollen spore. Intel is mass producing the 0.25 micron process technology. Next year, in 1999, a 0.18 micron technology will be in production, and we are already working in the lab on a 0.13 micron technology.

The third paper describes the challenges faced when shrinking transistors below the 0.13 - 0.10 micron range. Intel is now addressing these challenges in preparation for the turn of the millennium.

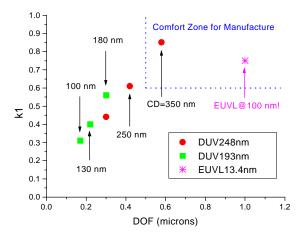

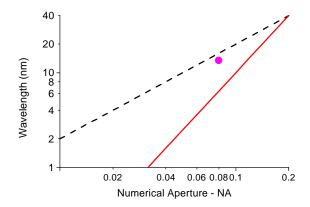

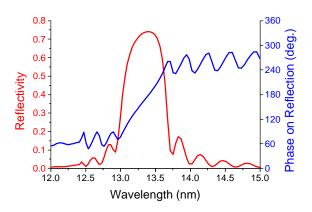

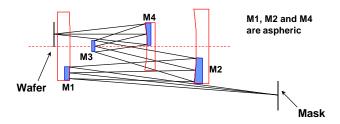

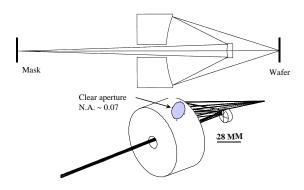

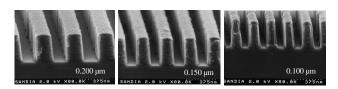

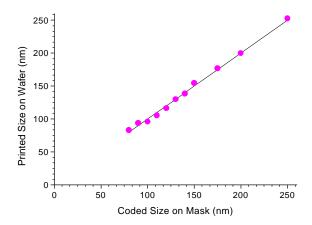

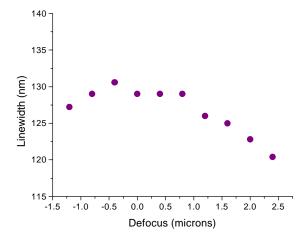

And finally, the fourth paper describes the future of lithography used to imprint very small patterns onto silicon wafers. Optical projection lithography is used today, but will not be able to imprint the ever finer patterns needed in the future. Over the next several years, a new lithographic technology needs to be developed that can print lines of 50 nanometers and smaller. Extreme Ultraviolet Lithography (EUVL) is one of the technologies being evaluated.

# Intel's 0.25 Micron, 2.0Volts Logic Process Technology

A. Brand, A. Haranahalli, N. Hsieh, Y.C. Lin, G. Sery, N. Stenton, B.J. Woo California Technology and Manufacturing Group, Intel Corp.

S Ahmed, M. Bohr, S. Thompson, S. Yang Portland Technology Development Group, Intel Corp.

Index words: CMOS, shrink, interconnect

#### **Abstract**

Process 856 is a 0.25μm-generation logic technology currently in volume manufacturing, which has been optimized for high performance, yield, and density. This process is being used to manufacture high performance products including the Intel® Celeron<sup>TM</sup> and Pentium® II microprocessors. The process has a high equipment re-use rate to reduce cost. Using the older equipment has increased the challenge of scaling to smaller pitch, particularly in the interconnect process. Transistor optimization allows volume production of Pentium II microprocessors at 450 MHz. High yield has also been achieved, both before and after a 5% linear shrink of the initial 0.25μm design rules.

#### Introduction

Process 856 (P856) is Intel's quarter micron (0.25 $\mu$ m) logic technology. In developing P856, the important goals were to achieve low cost through high equipment re-use, deliver a gate delay improvement of 30%, and deliver high yield. An equipment re-use goal of 70% was set: the actual level achieved was 85% [1]. A performance goal of 30% transistor delay improvement was set: this was exceeded by 18%. The yield improvement curve for the P856 is the fastest of any Intel process so far.

Each generation of high-performance, low-power microprocessor products requires progressively faster transistors with lower operating voltage, produced with higher density. Historically the rate of improvement in gate delay has been 30% per generation. Normally it takes two to three years to develop a new technology, and each technology generation is progressively more expensive. Through scaling and the introduction of key architectural features such as halo NMOS, P856

delivered a better than 30% delay improvement at certification, the key checkpoint for volume manufacturing.

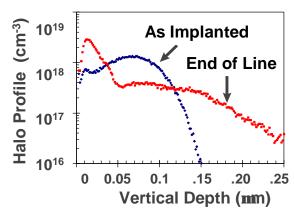

A second post-certification technology enhancement project delivered a 5% linear shrink with an additional 18% delay improvement, using the same equipment set. This represents nearly a half technology generation improvement in performance and yield, and it was delivered at very low cost. The post-certification improvement was achieved through control improvement and further transistor scaling, including a reduction of gate oxide thickness, enhanced halo processing, and general optimization of transistor implant conditions. This transistor enhancement has been critical in achieving good binsplit for Pentium II processors at 450 Mhz.

In this paper, we describe the important architectural features in P856 that enabled scaling of the interconnect process and transistor enhancement. The transistor improvements made in the pre- and post-certification stages are described. We discuss some of the important issues for interconnect processing with quarter micron features. We also describe the approach used to achieve a 5% shrink of the initial design rules.

# **Transistor Integration**

### **P856 Architectural Enhancement**

A fundamental constraint for short channel length transistors is that as the channel length is reduced to improve drive current, the barrier to off-state leakage is decreased. Throughout the development of P856, the transistor was optimized to achieve the best Idsat at a given margin to leakage, while also striving for low capacitance. High transistor performance in P856 was achieved through aggressive scaling to 40.8A electrical

gate oxide and sub-quarter micron poly dimensions, and through the addition of the following architectural enhancements, to be described in detail:

- Silicon pre-amorphization implants

- NMOS and PMOS halo implants

- Junction compensation implants

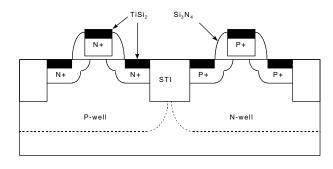

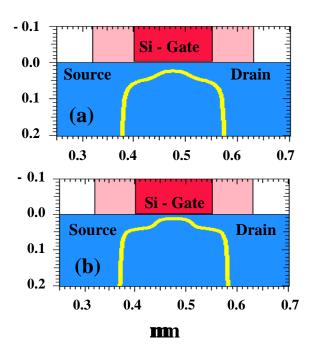

Like the previous generation P854 (0.35µm) CMOS process, the P856 process flow uses 200mm P-/P+ epi wafers and begins with shallow trench isolation followed by implantation of N and P wells. The gate oxide thickness is scaled from 60A on P854 to 40.8A on P856. Complimentary doped polysilicon is used to obtain matched Vt in N- and P-MOS devices. Nitride spacers are used to separate the deep source drain regions from the shallow source drain extensions. TiSi2 is selectively formed on polysilicon and source drain regions, obtaining a worst-case sheet resistance of 5  $\Omega$ /sq. The transistor structure is illustrated in Figure 1.

Figure 1: Schematic cross section of transistors

### **Silicon Pre-Amorphization Implants**

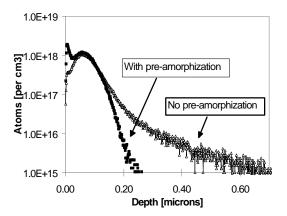

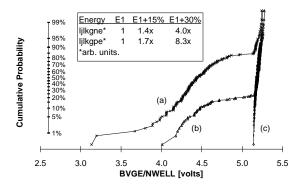

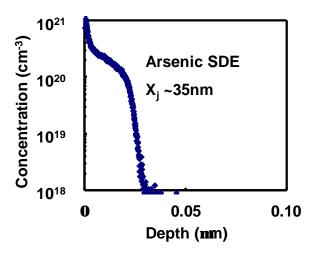

A silicon implant is introduced in P856 after poly gate definition. It is used to create an amorphous layer in the polysilicon gate and source/drain regions of both the N and P devices. The amorphous layer reduces the channeling tails of subsequent implant steps resulting in abrupt implant profiles (see Figure 2). Reducing the lateral implant tails under the poly gate region is key to controlling the sub-threshold leakage in short channel devices. The dose and energy of the Si implant need to be high enough to amorphize the underlying region without degrading the gate oxide. Figure 3 shows that gate oxide leakage increases for higher energy implant, and that gate oxide failure, as measured by lower breakdown voltage (BVG), can occur when the dose is too high. The table inset in Figure 3 shows the impact on gate leakage.

**Figure 2**: SIMS depth profile shows reduction in As implant tail due to Si pre-amorphization

**Figure 3**: Increased Si pre-amorphization dose reduces the gate breakdown voltage. BVG failure rate is shown vs. a) 2X PA dose, b) 1.5X PA dose, and c) nominal PA dose.

#### **NMOS and PMOS Halo Implants**

The short channel behavior of both NMOS and PMOS transistors was further enhanced by the introduction of halo implants. The halo implant is a high-angle implant introduced after Si pre-amorphization in the same lithography step used to dope the source/drain extension regions. Since the halo implant uses a high angle it must be done in four 90-degree rotations in the implant tool to ensure both sides of the channel are doped and that transistors oriented in both X and Y directions get doped. The halo implant uses the same implant type as the original well dopant (for example, N type dopant for the Nwell of the PMOS device).

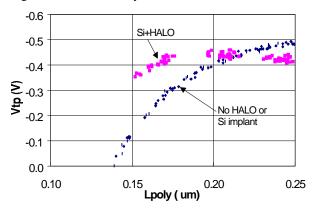

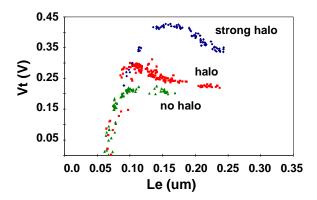

The halo implant, together with the well implant, sets the threshold voltage of the transistor. By reducing the initial well implant dose and introducing the halo implant after gate patterning, a non-uniform channel doping profile is achieved. Due to the angled implant, short channel devices receive a higher dopant concentration than do longer channel devices. There are several benefits when these implants are optimized. The halo implant reduces the Vt roll-off in short channel devices as shown in Figure 4. Since the same Vt is achieved with lower average channel concentration, the Vt with substrate bias is reduced as shown in Figure 5. Most important, higher Idsat at target is achieved because with a given Vt, the halo device has a more abrupt drain-channel junction and higher channel mobility than a non-halo device.

**Figure 4:** Reduction in PMOS threshold voltage roll-off with Si pre-amorphization and halo implant

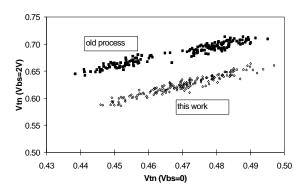

Figure 5: Reduction in substrate bias Vt effect

#### **Junction Compensation Implants**

The third major transistor modification on P856 is the use of compensation implants to reduce junction capacitance. AC parameters play an increasingly important role in overall transistor performance, and junction capacitance was a high leverage parameter contributing to the performance of P856. A compensation

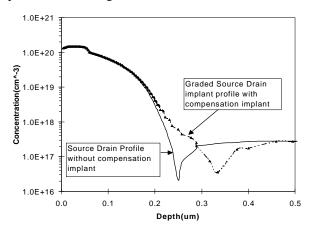

implant is introduced in both N and PMOS devices during the same lithography sequence used for source and drain (S/D) implants. This implant uses the same type species as the S/D implant but with a lower dose and higher energy to give a more graded implant profile at the junction (see Figure 6). The compensation implant conditions were chosen to give approximately a 20-30% reduction in junction capacitance (see Table 1) with no degradation of the isolation performance or the implant penetration of the gate oxide.

**Figure 6:** Junction doping profile with the addition of a compensation implant to reduce junction capacitance

| Type | Before     | With       | Change |

|------|------------|------------|--------|

| N    | 1.0 fF/µm2 | 0.7 fF/µm2 | -30%   |

| P    | 1.25       | 1.0 fF/µm2 | -20%   |

|      | fF/µm2     | ·          |        |

**Table 1:** Junction capacitance area component reduction attributed to compensation implants

#### **Transistor Performance Results**

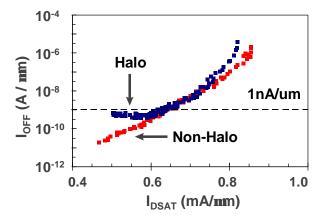

P856 was certified in Q3 1997 using halo implants, Si pre-amorphization implants, and n+ junction compensation [3]. Based on the common industry metric of 1nA/μm worst-case device leakage, the Idsat target of 0.585mA/μm for NMOS and 0.250mA/μm for PMOS was achieved. A simulated transistor delay metric known as FEM95 showed that the performance goal of a 30% delay improvement over P854 had been achieved.

| Time          | NMOS  | PMOS  | FEM95   | FEM95  |

|---------------|-------|-------|---------|--------|

|               | Idsat | Idsat | vs P854 |        |

| Certification | 0.585 | 0.250 | -33.2%  | ref    |

| Cert+2Q       | 0.670 | 0.295 | -45.8   | -18.8% |

| Cert+4Q       | 0.700 | 0.310 | -49.9   | -23.6  |

**Table 2:** Idsat target and FEM95 benchmark results as a function of time (in quarters) from certification (the FEM95 reference is P854)

To rapidly deliver significant additional performance, two process revisions were developed and implemented within a year of certification. The enhancement involved further thinning of the gate oxide to 40.8A, scaling of the poly target due to improved poly control, implementation of a p+ junction compensation implant, and reoptimization of the NMOS and PMOS halo, well, and S/D implants.

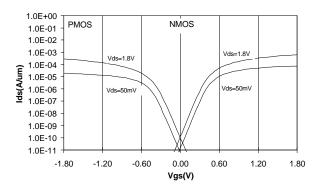

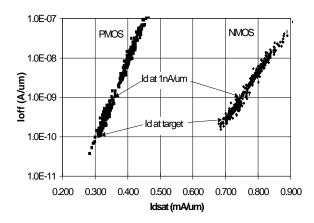

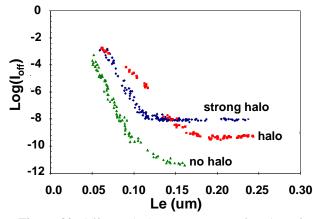

The halo implant re-optimization allowed a reduction in the N and P well surface implant, favoring an increase in the halo implant. The resulting transistors have well behaved sub-threshold characteristics (see Figure 7). As shown in Figure 8, we achieved Idsat at  $1nA/\mu m$  of  $0.755mA/\mu m$  for NMOS and  $0.350mA/\mu m$  for PMOS. Accounting for the channel length control margin, we achieved industry pace-setting Idsat at target of  $0.700mA/\mu m$  for NMOS and  $0.310mA/\mu m$  for PMOS [4],[5]. These results are summarized in Table 2.

**Figure 7:** IV sub-threshold characteristics for NMOS and PMOS devices for target devices

**Figure 8:** NMOS and PMOS drive current vs. leakage (the reference leakage current is 1nA/μm)

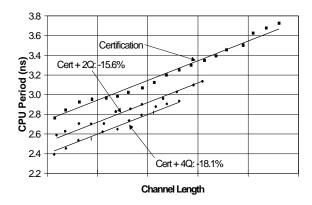

The improvement in performance has been demonstrated using the Pentium II microprocessor. Maximum speed measurements made at low-voltage and low-temperature

conditions primarily show the improvement made in transistor performance. Under these conditions there is little influence from interconnect RC delay, because the interconnect sheet rho is reduced at low temperature. Figure 9 shows the progression in microprocessor path delay (period) as a function of time from certification. (In this figure, the data is smoothed for clarity, and the same stepping and test program is used in all cases.) A net 18.1% delay improvement has been observed on the same stepping of the Pentium II microprocessor. While there is dilution of the transistor improvement due to RC limited paths, with this enhanced process, better than 50% Fmax improvement has been achieved in microprocessor speed compared to the prior 0.35µm technology [6].

**Figure 9:** Microprocessor low voltage/low temperature delay improvement from post-certification process enhancement

All of the benchmarks discussed in this section are based on 1.8V transistor test conditions, and the P854 reference assumes the P854 and P856 run under nominal 2.5V and 1.8V conditions. To enable further performance enhancement, the reliability characterization of P856 was converted to a 2.0V nominal criteria. On products that can tolerate higher power consumption due to increased voltage, the 2.0V operation supply improves performance. Microprocessor characterization shows that there is an additional 9-10% frequency enhancement at 2.0V compared to 1.8V. At certification, P856 met the reliability goals for 2.0V operation.

#### **Interconnect Integration**

P856 uses five metal layers that are optimized for microprocessor performance and density. Table 3 shows the intended functions for each layer. Intel's technologies for logic are optimized for high aspect ratio to provide the most competitive RC performance at the

best density. The M1 to M3 layers use tight pitch, which is necessary for good SRAM and logic cell routing density. The M4 and M5 layers use wide pitch and high thickness, resulting in the low sheet rho needed for power distribution and cross die interconnect.

As with previous Intel processes, the metal stack is Ti/Al-Cu/Ti/TiN, which provides low line and via resistance while meeting electromigration requirements. Also, as before, the first inter-layer dielectric (ILD) above poly is Boro-Phosphosilicate-Glass (BPSG). The BPSG is planarized using chemical-mechanical polishing (CMP). The remaining ILD layers are PTEOS oxide that use a deposition followed by an etch-back process followed by CMP planarization. The CMP steps improve layer planarity, which is necessary for the uniform lithographic and etch processing of multi-layer interconnects. Contacts and vias are all filled with tungsten plugs formed by blanket tungsten deposition followed by CMP.

| Layer | Pitch  | Thick  | AR  | Purpose                |

|-------|--------|--------|-----|------------------------|

|       |        | ness   |     |                        |

| M1    | 608 nm | 480 nm | 1.6 | local connections      |

| M2    | 882    | 900    | 2.0 | intermediate length RC |

| M3    | 882    | 900    | 2.0 | intermediate length RC |

| M4    | 1520   | 1325   | 1.7 | power / long RC        |

| M5    | 2432   | 1900   | 1.6 | power / long RC        |

**Table 3:** Metal layer pitch, aspect ratio, and intended applications

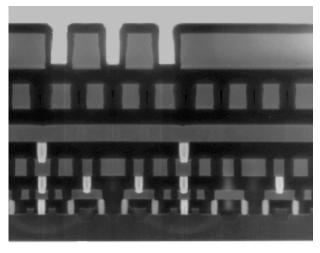

Figure 10: Five-layer metal interconnect cross section

To achieve cost savings, most of the metal-processing tools used in P856 were used in P854. The same stepper, metal deposition, contact etcher, metal etcher, and planarization equipment are used. A key challenge in the P856 interconnect has come from optimizing the lithographic and etch processes to work with the 20% smaller pitch of P856.

Just as Poly stretches the line width capability of DUV tools, Metal 1 patterning challenges the DUV lithography for space-limited capability, as the minimum space required is beyond the wavelength limits. This tight pitch (608 nm) demands thin photoresist for resolution, which in turn degrades the margin for metal etch due to resist erosion. The resist erosion results in poor metal line profile (shelving) and poor metal line critical dimension (CD) control.

Stringent control in depth of focus is also needed to ensure the integrity of the lithographic patterning. In order to achieve a planar surface for metal lithography, CMP is used prior to metal deposition for both ILD0 and contact plug steps. However, density variation causes local ILD erosion during CMP, which can result in severe variation in topography. For example, a depression as deep as 180 nm has been seen on the surface near a boundary between a dense memory array area and a loose periphery area. This depression causes a local area to be printed out of focus and results in a distorted metal line, as shown in Figure 11. Improved oxide and tungsten polishes that reduce the topographical step have been developed to ensure enough depth of focus on the surface.

**Figure 11:** Metal 1 line distortion caused by ILD erosion induced out of focus lithography

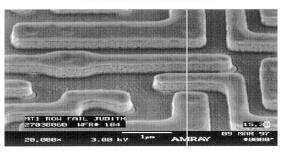

Another limitation of lithographic capability is evident in the pullback at the end of a metal line. This pullback can cause a reliability problem when it is so severe that the metal line does not adequately cover a contact at the end of the metal line. Figure 12 shows a Metal 1 void bake failure due to Metal 1 pullback and improper contact coverage. Twenty to 160 nm pullback has been detected in Metal 1 lines, depending on whether the structure is nested or isolated and on the location on the wafer. One solution to this pullback problem is to use optical proximity correction (OPC). These features compensate for the lithographic pullback effect at the end of the metal line. Contact coverage better than 75% has been achieved with OPC improvement, and the failure has essentially been eliminated.

**Figure 12:** Example of a Metal 1 void failure due to pullback, before process optimization

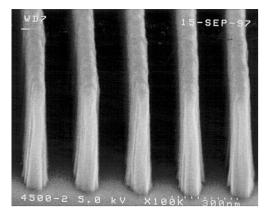

The P856 technology also places stringent demands on the metal etch control. Magnatron current and RF power are optimized to reduce the erosion of photoresist during etch and to provide enough sidewall passivation to protect the metal profile. A vertical Metal 1 profile without undercut and shelving was achieved while providing good metal CD control (Figure 13). In the high aspect ratio M1 process, incomplete etching due to cross wafer thickness and CD non-uniformity can result in metal stringer defects. This is addressed by limiting the M1 sputter deposition target lifetime, controlling the M1 grain size through minimum deposition chamber heating, improving the uniformity of metal thickness, reducing the metal electrical CD, and slightly increasing the over-etch time.

**Figure 13:** Metal 1 profile before optimization (top) showing shelving and M1 pullback, and after optimization (bottom) with good vertical profile & good contact coverage

Just as Metal 1 challenges the DUV limits, the Metal 2 and Metal 3 patterning with very thick films stress the Iline lithography limits. Both metals required significant improvements on processing issues, such as shelving of the metal profile, pullback at the end of metal lines, and bridging between narrow spaces. Optimized operating conditions have been determined for individual I-line lithographic tools to provide the best focus and exposure window. Together with an optimized metal-etching recipe, shelving is eliminated in the metal profile. Optimized reticle sizing for narrow spacing is used to provide adequate margin for the metal bridging. OPC is also used in Metal 2 and Metal 3 reticles to reduce pullback. The combination of these enhancements has successfully provided needed process capability in a production environment.

#### 5% Shrink

A 5% linear shrink, known as P856.5, was applied to P856.0 in order to reduce die cost. A 5% technology shrink has been used in Intel in many generations as a standard means of cost reduction. Due to high equipment re-use in P856, the margin for shrink initially appeared tighter than in previous technologies. This required increased optimization of individual layers. Process margins and design rule margins were examined closely in order to achieve a "smart shrink" for minimum margin loss on the tightest part of the technology.

The smart shrink strategy uses optimum sizing for all critical layers and optimum targeting for critical

dimensions. For example, the high performance interconnect has high aspect ratio metal spacing as well as lines. The lithographic and etch margins are more critical for spacing than for lines in manufacturing. Therefore, a strategy of avoiding or minimizing shrinking metal spacing was adopted. Whenever possible, the metal line width rather than the space is shrunk. This helps ensure no degradation in speed due to the increased cross-talk if spacing were shrunk.

The reduced metal line width in the shrink technology does reduce certain design rule margins such as metal overlap of underlying via and metal enclosure of top via. To overcome this difficulty, OPC techniques were used creatively to systematically prevent the degradation of the design rule margin. For the contact layer, the proximity effect from clustered contacts became much worse after shrink, and a special selective sizing method was used on the reticle to restore the process margin. Due to very many layers tight constraints. required characterization. Table 4 shows the approaches used for critical DUV and I-line layers.

| Layer     | Shrink       | Re-           | Mask             |

|-----------|--------------|---------------|------------------|

|           | Strategy     | Characterized | Fix/OPC          |

| Isolation | Line / Space | Yes           | No               |

| Poly Gate | Space        | Yes           | OPC              |

| Contact   | Space        | Yes           | Selective sizing |

| Metal 1   | Mostly line  | Yes           | Improved OPC     |

| Via 1     | Line /Space  | Yes           | No               |

| Metal 2   | Mostly line  | Yes           | Improved OPC     |

| Via 2     | Space        | No            | No               |

| Metal 3   | Mostly line  | Yes           | Improved OPC     |

Table 4: Shrink strategy

The shrink reduces SRAM cell size from  $10.26\mu m^2$  to  $9.26\mu m^2$ . With the 5% shrink, there is a 15% increase approximately in sorted good die due to smaller die size. The shrink technology went to production four months after product tape-out thereby setting a new benchmark. All quality and reliability requirements were met, and products were synchronized just in time for the volume production ramp.

#### Conclusion

At certification, P856 met its principal performance, yield, and density goals, while achieving an 85% equipment re-use rate. Within one year of certification, and with only low-cost changes, a further 5% shrink was

implemented. With the same equipment set, reoptimization of the transistors combined with control enhancement has allowed an 18% improvement in gate delay, more than a half technology step.

# Acknowledgments

Many people contributed to the results discussed in this paper. Key people include Max Wei, Brian Johnson, Maurice DeCourcy, Domenic Pipitone, Karen Lubic, Brett Huff, Haiping Dun, Sam Hu, Bill Kavanaugh, Yung-Huei Lee, Wallace Lin, Steven Soss, Andrew Stack, John Mardinly, Li-Jia Ma, K.C. Patel, Tom Castro, Nevine Malek, Mike Maxim, Melinda Hoppe, and Ajay Chatterjee. In addition to those mentioned, we acknowledge the contributions of many others from the CTM, PTD, and virtual factory module and integration groups.

#### References

- [1] M. Bohr, Y. El-Mansy, "Technology for Advanced High-Performance Microprocessors," *IEEE Transactions on Electron Devices*, March 1998, pp. 620-625.

- [2] S. Wolf, Silicon Processing for the VLSI Era, Volume 3: The Submicron MOSFET.

- [3] M. Bohr, S.S. Ahmed, S.U. Ahmed, M. Bost, T. Ghani, J. Greason, R. Hainsey, C. Jan, P. Packan, S. Sivakumar, S. Thompson, J. Tsai, and S. Yang, "A High Performance 0.25um Logic Technology Optimized for 1.8V Operation," *IEDM Technical Digest*, 1996, pp. 847-850.

- [4] S. Venkatesan, A. Gelatos, B. Smith, R. Islam, et.al., "A High Performance 1.8V, 0.20um CMOS Technology with Copper Metallization," *IEDM Technical Digest*, 1997, pp. 769-772.

- [5] M. Chang, J. Ting, J. Shy, L. Chen, "A Highly Manufacturable 0.25 um Multiple-Vt Dual Gate Oxide CMOS Process for Logic/Embedded IC Foundry Technology." 1998 Symposium on VLSI Technology Digest, pp. 150-151.

- [6] J, Schutz, R. Wallace, "A 450MHz IA32 P6 Family Microprocessor," *ISSCC Technical Digest*, 1998, p. 236-237.

# **Authors' Biographies**

Adam Brand received his BSEE and his MSEE from the Massachusetts Institute of Technology in 1991. He joined Intel in 1991 and is currently working in the California Technology and Manufacturing  $0.25\mu m$  Device Group. His interests include transistor

performance optimization, high voltage device development, and circuit modeling. His email address is adam.d.brand@intel.com.

Aravinda Haranahalli received an MS in Physics in 1976 and a Ph.D in Materials Engineering 1980 from the University of Florida. He joined Intel in 1984 and has held various management positions in technology, manufacturing, and business development. He currently manages interconnect technology development for 0.2µm. Before joining Intel he held technology positions at Texas Instruments and Fairchild. His current interests include technology, manufacturing, and business management. email address His is aravinda.r.haranahalli@intel.com.

Ning Hsieh received a Ph.D. in Materials Science from Northwestern University in 1979. He worked for various semiconductor companies including IBM, Fairchild, and DEC. He joined Intel in 1993 and has worked in CTM Technology Development since then. His work experience is mostly in process integration. He has published six external papers and has six patents. His email address is ning.hsieh@intel.com.

Yi-Ching Lin graduated from the University of California, Berkeley with a Ph.D. in EECS in 1981. Prior to joining Intel in 1987, he was with Texas Instruments and Monolithic Memories, Inc. He has been working in the area of process integration for microprocessor, Flash and EPROM memories. He had also worked on technology transfer from D2 to foreign foundries, including those located in Taiwan and Japan. His email address is yi-ching.lin@intel.com.

George E. Serv is an Intel Fellow and director of Device Optimization Technology in Intel's California Technology and Manufacturing group. Mr. Sery is currently responsible directing process for characterization, performance improvement, capability enhancement for Intel's 0.25 micron CMOS logic technology. He received a B.S. and M.S. in electrical engineering from the University of Minnesota in 1976 and 1978 respectively. He joined Intel in 1978 as part of the SRAM Technology Development group. He has been involved with the development of NMOS and CMOS technologies for logic, SRAM, and Flash memory applications. For each technology, he has led the device physics team responsible for device development and process characterization. His email address george.sery@intel.com.

Nicky Stenton received a M.S. in Materials Engineering from Lehigh University in 1982. She joined Intel in 1982 and most recently has been working on transistor process development in the California Technology and

Manufacturing P856 Integration group. Her email address is nicky.stenton@intel.com.

Been-Jon Woo received a B.S. in Chemical Engineering from the National Taiwan University in 1975 and a Ph.D. from USC in 1979. She joined Intel in 1984 after working at Fairchild. She has worked in EPROM, Flash, and logic technology integration in the California Technology and Manufacturing group. She is currently the 0.25µm transistor integration manager. Her email address is been-jon.k.woo@intel.com .

Shahriar Ahmed joined Intel in 1985, initially as a interconnect device engineer working on Process 448. He subsequently was part of the team that developed P648 and coordinated the final transfer to high-volume manufacturing. Shahriar then moved on to be the device engineer for Intel's first bi-CMOS process. His next project was P856, which he developed together with a team from California Technology and Manufacturing. Currently he is in working on 0.18µm process development. His email address is shahriar.ahmed@intel.com

Mark T. Bohr joined Intel in 1978 after receiving a MSEE from the University of Illinois. He has been a member of the Portland Technology Development group since 1978 and has been responsible for process integration and device design on a variety of DRAM, SRAM, and logic technologies, including recently 0.35  $\mu$ m and 0.25  $\mu$ m logic technologies. He is an Intel Fellow and director of process architecture and integration. He is currently directing development activities on 0.18  $\mu$ m and 0.13  $\mu$ m logic technologies. His email address is mark.bohr@intel.com .

Scott Thompson joined Intel in 1992 after completing his Ph.D. under Professor C. T. Sah at the University of Florida on thin gate oxides. He has worked on transistor design and front-end process integration on Intel's 0.35, 0.25, and 0.18  $\mu$ m silicon process technology design for the Pentium® and the Pentium® II microprocessors. Scott is currently managing the development of Intel's 0.13  $\mu$ m transistor design. His email address is scott.thompson@intel.com .

Simon Yang received his B.S. in Electrical Engineering from the Shanghai University of Science and Technology (Shanghai, PRC). He then received his M.S. in Physics and a Ph.D. in Materials Engineering from the Rensselar Polytechnic Institute in New York. He joined Intel after graduating in 1987 and is currently leading transistor and yield improvement for Intel's 0.18µm logic technology. His email address is shining.yang@intel.com.

# The Quality and Reliability of Intel's Quarter Micron Process

Krishna Seshan, Technology and Manufacturing Group, Intel Corp.

Timothy J. Maloney, Design Technology, Intel Corp.

Kenneth J. Wu, Technology and Manufacturing Group, Intel Corp.

Index words: quality, reliability, ESD protection, electromigration, mechanical stress

#### **Abstract**

This paper describes how the quality and reliability of Intel's products are designed, measured, modeled, and maintained. Four main reliability topics: ESD protection, electromigration, gate oxide wearout, and the modeling and management of mechanical stresses are discussed. Based on an analysis of the reliability implications of device scaling (the process of a planned reduction of dimensions and operating parameters), we show how these four topics are of prime importance to component reliability. We conclude with a brief discussion of the future challenges of energy scaling.

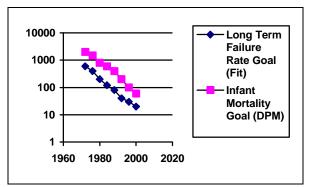

#### Introduction

The maintenance of quality and reliability is an important aspect of Intel's product goals. Intel's goal for reliability is to strive to reach failures-in-time (FITs) to less than the hundred range by the end of the century. FITs are defined as the number of device failures in 1.0E9 or billion device hours. In order to reach this goal, defects have to be reduced to less than 100 ppm. For more details refer to Intel's *Component Quality and Reliability Handbook* [1]. Intel's reliability goals are shown in Figure 1.

**Figure 1:** Failure rate (FIT) & defect rate (DPM) goals (the top curve represents infant mortality goals, which can only be achieved by reducing defects)

In this paper we discuss four of the main topics pertaining to the maintenance of reliability for the  $0.25\mu m$  process also known as P856 so that Intel meets its product goals. The topics are as follows:

- 1. electrostatic discharge (ESD) protection

- 2. electromigration failures resulting from increased current densities

- gate oxide wearout failures resulting from decreasing gate oxide thickness

- modeling and management of the effects of mechanical stress resulting from silicon-package interactions

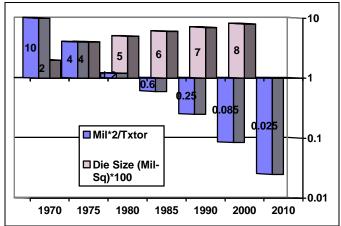

There are two major challenges to maintaining quality and reliability. The first is the continued increase in die size. Even though transistor density increases, new features and functionality are added to the microprocessor causing die size to grow. This is depicted in Figure 2, which shows the size growth of Intel's products. Some of the microprocessors using the 0.25µm process generation are as large as 800 mils on the side and have in excess of seven million transistors.

**Figure 2:** The continued growth of the microprocessor despite the increase in transistor density

The die sizes and the area per transistor for the products shown in Figure 2 are plotted generationally in Figure 3.

The graph shows the decrease in area per transistor (mil\*2/transistor) that has enabled the three-fold compaction per decade. Also plotted is the die size in Mil -Sq. This is the square root of the area. Note that die size increases generationally, and that die sizes as large as 800 mils-square are allowed by the reliability envelope.

**Figure 3:** Generational graph of area per transistor and die size trends (increase in functionality contributes to the increase in die size)

As microprocessors grow in complexity, Intel's customers have come to expect improved reliability. The reliability of devices and packaged products is measured by subjecting devices to various reliability tests aimed at accelerating failures. The results of these tests are then displayed in a graph such as is shown in Figure 1.

#### **Reliability Implications of Scaling**

Before going into detail on the four reliability topics mentioned, we briefly discuss scaling and its implications on reliability.

Scaling is the process by which device dimensions are reduced or "scaled" from one process technology to the next. Continued scaling of transistors to improve speed results in increased frequency and this in turn requires an increase of current density in metal lines and vias. This increase accelerates failures by electromigration. As metal line dimensions are decreased, so is gate oxide thickness. The resulting thinner gate requires carefully designed protection against electrostatic discharge events. The thinner gates also suffer from the effects of wearout caused by the hot electron bombardment of the gate oxide. In order to provide increased protection, the operating voltage was decreased or "scaled" to 2.0 volts. This then leads to a decrease in current density and offsets the increase in frequency. A second level of protection is obtained by using design rules based on an

understanding of the electromigration failure mechanisms.

Various aspects of quality and reliability constitute the so-called "Reliability Envelope." As device length L scales, various parts of this envelope scale as "K," where K is the scaling factor and is > 1. Therefore, the channel length would scale by L\* (1/K). Table 1 shows several parameters of this envelope that will scale "ideally." Table 2 shows how "ideal scaling" applies to various aspects of reliability of the integrated circuit.

| Scaling factor K>1      | Ideal<br>Scaling | Reliability<br>Implications       |

|-------------------------|------------------|-----------------------------------|

| Channel Length L        | 1/K              | Latchup                           |

| and shallow junctions   |                  | Hot-electron effects              |

| Gate Oxide<br>Thickness | 1/K              | Oxide wearout and ESD protection. |

|                         |                  | Process Charging                  |

| Metal line width        | 1/K              | Electromigration                  |

**Table 1:** Reliability impacts on ESD, electromigration, etc. caused by ideal scaling (note that this table only deals with "ideal" scaling on device dimensions)

The most important consequence of the data from Table 1 is that in order to maintain a constant "E\_Field" and preserve gate oxide reliability, (that is, maintain the electric field across the gate) *operating voltage must be scaled.* This leads to so-called "supply voltage scaling" that is shown in Table 2.

Table 2 shows the main implications to component reliability from scaling: ESD, gate oxide wearout, electromigration, and stress.

| Electrical<br>Parameter | Ideal Scaling<br>with Scaled<br>Supply Voltage | Reliability<br>Implications of<br>Scaling                                              |

|-------------------------|------------------------------------------------|----------------------------------------------------------------------------------------|

| Operating<br>Voltage    | Vcc * 1/K                                      | Hot e and gate oxide reliability are rendered equivalent in the scaled voltage scheme. |

|               | T                | ı                  |

|---------------|------------------|--------------------|

| Device        | 1/sqrtK - 1/K    |                    |

| Current       |                  |                    |

|               |                  |                    |

| Metal Current | K**1.5           | EM, and self       |

| Den           |                  | heating increases. |

|               |                  |                    |

| Die Size      | Does not scale   | Package stress     |

|               |                  | effects on metal   |

|               |                  | lines and          |

|               |                  | dielectric layers. |

|               |                  | diciectife layers. |

| Mechanical    | Does not seem to | Stress effects on  |

| stress from   | scale            | Devices and        |

| die-package   |                  | interconnections.  |

| interactions  |                  |                    |

| interactions  |                  |                    |

| Power         | 1/k**1.5         | Total power does   |

|               |                  | not scale with Vcc |

| dissipation   |                  | This creates       |

| per gate      |                  | challenges for     |

|               |                  | 0                  |

|               |                  | cooling.           |

| Gate Delay τd | 1/k**1.5         | Main contributor   |

| Saic Delay tu | 1,11             | to performance     |

|               |                  |                    |

|               |                  | enhancements.      |

| Delay x       | 1/k**3           | Even though        |

| Power         |                  | power delay per    |

| 10001         |                  |                    |

|               |                  | gate scales, total |

|               |                  | power does not.    |

|               |                  | 1                  |

**Table 2:** Impact of dimensional scaling on device electrical parameters with a scaled supply voltage

As can be seen from Table 2, some parameters do not scale at all, notably current and size. This has a significant impact on the amount of scaling that can occur. Reliability is affected by scaling because scaling gives rise to larger current densities, higher chip temperatures, and higher electric fields during device operation. However, if Vcc and process are both scaled, then electric field (E) can be maintained invariant. This then begs the question of how low Vcc can be scaled and how much power dissipation can be lowered? This question is dealt with in the Discussion section at the end of this paper. Other parameters such as stress and power that do not scale even with the scaled supply voltage are also discussed in the Discussion section.

We now return to the discussion of the four main topics of component reliability: ESD protection, electromigration, gate oxide wearout, and modeling and management of mechanical stress. These four topics are presented below with an introduction in the beginning aimed at the general reader in each topic.

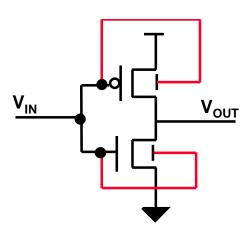

# Aspects of Electrostatic Discharge (ESD) Protection

In recent years, CMOS FET scaling, power supply voltage scaling, and FET engineering for performance have caused a continued need for ESD protection methods that can be easily applied to inputs and outputs, without interfering with process development. Despite the scaling of devices to submicron dimensions, where oxides break down at, say, 5V, and junctions and wells are shallower, the ESD test goals are the same (e.g. 2000V human body model). How have designers been able to achieve the same ESD performance with the new devices? The ideal low-cost ESD design exploits devices that are available "for free" as part of the process, and which do not need to be engineered for ESD performance and then made compatible with other goals. We will discuss how these ambitious design goals are met for the 0.25µm process.

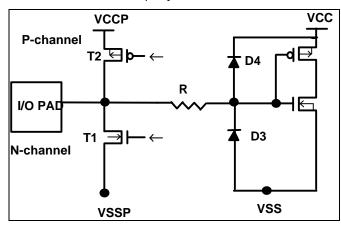

To understand these protection methods, we define smooth ESD current paths through the chip for the possible ESD events in stress testing and in actual handling. The natural diodes to power and ground are used, and current paths are linked together with the help of power supply clamps. The latest designs for power supply clamps in the 0.25µm process technology take full advantage of device scaling, which only in recent years has made it possible to dissipate ESD-scale currents (on the order of amperes, but only for nanoseconds) within small amounts of chip area (bond pad size) by using MOS FET conduction. In earlier days, some kind of avalanche breakdown event had to be used, but sensitivity to process and triggering events made these methods very difficult to execute. With dual diodes for basic inputs and outputs, and special PMOS FET circuits for power supply linkage, smooth ESD current paths can be defined for nearly all varieties of chip interface with the outside world. PMOS FET clamping methods for ESD have become important for all of Intel's low voltage deep submicron CMOS products. They also help to solve the ESD protection problems for mixed voltage products, where compatibility with signals from earlier technologies is desired.

#### ESD Protection Issues for 0.25µm Process

The scaling of power supply voltages below 5V in recent years has meant that components need to be backward compatible, to some extent, with chips running on higher voltage supplies. Table 3 summarizes the situation with four typical CMOS integrated circuits processes of the past few years, with Proc1 being the last of the processes allowing a continuous 5 volts across the gate oxide.

Proc4 is the 0.25µm process, under discussion here.

Many designers use (what might be called) the dual diode principle as much as possible in their chips. example, a typical CMOS input/output (I/O) pad such as in Figure 4 has driver devices T1 and T2, which have parasitic diodes to power and ground resembling the dual diodes of an input-only. Even though the NMOS T1 FET might have its source on a separate Vssp supply as shown in Figure 4, its diode to Vss (substrate) is a particularly good one if the CMOS process is on epitaxial silicon with a conducting p+ substrate (as used on Intel's 0.25µm process. This diverts most of the current in one polarity of ESD pulse. The other polarity is steered toward T2's inherent diode to Vccp, which can be optimized (or even augmented) through obvious layout methods. Thus not much current is being handled by the breakdown mode of the NMOS T1 device. In recent years, the NMOS device has become weaker and weaker in ESD due to self-aligned silicide (salicide) on the drain and source, and also because of lightly doped drain (LDD) structures. Even when salicide is blocked between drain and gate with a section of n-well [2], it is best to use dual diode current steering and avoid much breakdown current flowing through the T1 transistor during ESD. For that reason, dual diode methods are commonly used on outputs as well as inputs.

The final link in the ESD protection scheme is that between one power supply and another. Much work on the use of diodes for cross-linking similar power supplies has been done by Intel [3]. Less obvious is how to clamp dissimilar power supplies, such as Vcc to Vss. These stand-alone power supply clamps also can solve the problem of powerup sequencing (as when "similar" Vccx power supplies are powered up and may overstress their crosslinking diodes) and they have become increasingly popular as a result of their success.

| 5.0V         | 3.3V         | 2.5V    | 1.8-<br>2.0V |

|--------------|--------------|---------|--------------|

| Proc1        | Proc1<br>low |         |              |

| Proc2 hi     | Proc2        |         |              |

| Proc3<br>hi+ | Proc3 hi     | Proc3   |              |

|              | Proc4<br>hi+ | Proc4hi | Proc4        |

**Table 3:** Compatibility of sub-micron CMOS technology: Proc1 is the last 5V process, Proc4 is the 0.25μm process

**Figure 4:** CMOS Input/Output buffer protection (T1 and T2 have built-in parasitic dual diodes that can be enhanced through layout)

Work at Intel in the 1992-95 time frame pointed toward the need for power supply clamping in ESD protection, and to the need for a design that would yield equivalent or better performance with each process generation. Our rigorous qualification standards required universal application of power clamp cells, meaning that each clamp should pass all standard ESD tests with some margin (>4-8kV HBM, >1.2kV CDM) in stand-alone mode, so that an arbitrarily small power supply would be protected. In addition, pulsed I-V behavior must be consistent with sinking at least a 2kV HBM peak current (1.33 amps) below the known danger Vcc voltage for all ordinary circuits in the process, even vulnerable ones (it was expected that every supply would have at least two clamps). These criteria, and the cost-driven desire not to add masks or tamper with the performance-engineered FET process, drove us away from NMOS FET clamps [4,5] because the salicided devices, even large ones, failed miserably on all ESD tests. Unsalicided NMOS devices resembling Worley's [5] had the same problems with size and CDM behavior.

However, the properties of power clamps made from PMOS FETs [6] were quite favorable. Dimensions at or near minimum could be used, so the disadvantage of PMOS current drive per unit gate width over NMOS was hardly noticeable. The PMOS devices (pmosclamps) in this driven-gate mode were very rugged in all the aforementioned ESD and pulsed I-V tests, sometimes almost impossible to destroy. We did not have to intervene in the performance-oriented process development cycle with wafer splits and such; we just

evaluated the process changes as they happened to confirm continued good performance. As the PMOS FET is free of the positive feedback and negative differential resistance effects of npn snapback [8], it appears to have no difficulty conducting uniformly over a large area, even in the high-voltage breakdown regime. The results discussed here are from devices fabricated on  $0.35\mu m$  and  $0.25\mu m$  processes, now in manufacturing. Some details of the processes have been released publicly [8,9].

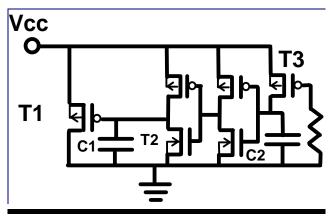

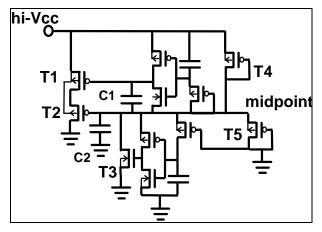

The basic pmosclamp (Figure 5) is built around a large (around 3000µm) p-channel transistor (T1) of nearminimum gate length. Its gate is driven temporarily to ground in two ways. First, a MOS capacitor (C1) helps to overcome the capacitive coupling of the large gate to Vcc. But more important, the inverter driving the T1 gate is heavily weighted toward the NMOS device, T2, pulling the T1 gate low with considerable strength. The RC timer formed from T3 (long channel) and C2 sets the time constant (microseconds), while the first inverter trip point is set midway between ground and Vcc for high noise immunity.

**Figure 5:** RC-timed circuit for PMOS FET power clamp (pmosclamp); T2 and C1 enhance gate drive

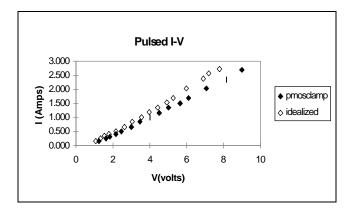

Figure 6 shows pulsed I-V curves for a pmosclamp protection circuit as in Figure 5, occupying about 7700  $\mu$  m² in a 0.25  $\mu$ m process. The "idealized" curve is from a test pattern with the T1 gate artificially hard-wired to Vss, and it shows how close we come to the desired grounding of the gate during the pulse. The I-V of a pmosclamp without the optimized trigger circuit including C1 and T2 (data not shown) shows clearly degraded characteristics as the gate does not fully turn on. The gate length used in Figure 3 matched for the two examples shown and happened to be well above the process minimum; the pmosclamp now routinely used in products has about a 10% higher pulsed current than

shown, and its gate length is still substantially above the process minimum. The sub-threshold leakage of these pmosclamps is not an issue; it is below 1  $\mu$ A until considerably above 100 C. The clamps were also shown to be robust against power supply noise, which was simulated on test chips with a high-frequency signal applied to the power supply node. There have been no reliability problems with the clamps on recent products.

Simulations of these circuits (using the standard process MOSFET model) match the pulsed I-V curves almost perfectly to the device model's voltage limit of 4-5V. Note how the pmosclamp continues to conduct (without destruction) up to 9-10V, far beyond the observed dc punchthrough voltage, around 5-6V. Thus the HBM self-protection of these clamps was measured at 8 kV, and CDM did not fail to the limit of the 2kV Keytek socketed tester. This is a hopeful sign for CDM protection of products as well. The empirical product results are very good so far.

The equivalent pmosclamp for the 0.35µm process has roughly the same I-V curve as in Figure 6, and it is in a still-reasonable 12000µm<sup>2</sup>, but this uses over 50% more area than the 0.25µm process. The trend should continue until such MOS conduction of pulsed currents runs into thermal limits. All of this is because, with shorter FET channels, we can achieve more pulsed and dc current sinking per unit area as processes scale. In the days of process feature size of 0.8µm and above, the same PMOS FETs for sinking ESD currents would have been absurdly large. However, just in the past few years, it has become possible to sink more than an ampere of pulsed current through ordinary MOS conduction in a production PMOS FET less than the size of a bond pad. Moreover, while devices have scaled dramatically due to Moore's Law, ESD events have not—the human being, source of the HBM, has not scaled noticeably (!), and electronic packages, source of the CDM, have proliferated into a variety of sizes and shapes, the CDM event is roughly the same as always. Thus device scaling once again teaches us to be on the lookout for opportunities as well as drawbacks.

**Figure 6:** Pulsed I-V behavior of pmosclamp in 0.25μm process; idealized curve has T1 gate artificially grounded

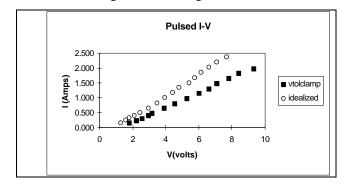

For compatibility with signals from chips with earliergeneration power supply voltage, we want to enable an on-chip power supply Vccx, greater than the voltage that can be safely applied for long-term reliability to a gate oxide in the process. A stand-alone solution is often desired, allowing Vccx to be on when Vcc is off. This is allowed with the stacked pmosclamp (vtolclamp) as shown in Figure 7. There are two large (about 4000µm in the 0.25µm process) p-channel devices in the same nwell, with no required contact to the common node, thus allowing tight layout. The midpoint voltage of approximately Vccx/2 is set by long channel devices T4 and T5. This reference voltage allows only Vccx/2 to be dropped across any of the gates in the circuit. The trigger circuits were modeled after those in the pmosclamp, where the capacitors and NMOS FETs pull the gates as low as possible, and RC circuits time them out.

The ESD and TLP (Figure 8) performance of the vtolclamp was on par with the pmosclamp for both the 0.35  $\mu m$  and 0.25  $\mu m$  processes, with device sizes scaled similar to the pmosclamp as described earlier. About twice as much area was used for the vtolclamp due to conservative layout and circuit design. Prospects are good for compaction of the layout and for use of more aggressive circuits, improving the current per unit area of the vtolclamp in the future by perhaps 30-50%.

**Figure 7:** Circuit for stacked-gate high-voltage tolerant PMOS clamp (vtolclamp). T1 and T2 are large FETs built in the same n-well; circuitry drives their gates low temporarily. T4 and T5 bias the midpoint, rendering dc gate oxide voltages safe.

**Figure 8:** Pulsed I-V of vtolclamp in 0.25μm process; idealized curve has T1 and T2 gates artificially grounded

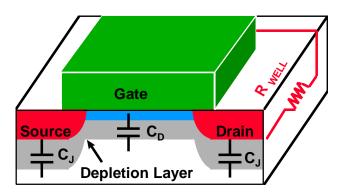

# **Electromigration**

Another reliability concern is electromigration. Electromigration failures result from increased current densities. The current generation of highly integrated microprocessors, requiring dense interconnects and large amounts of current, has highlighted the concern for metal interconnect reliability. Formation of metal voids induced electromigration during microprocessor operation will cause an interconnect open or high resistance resulting in malfunction or speed degradation.

The continued scaling of transistors for speed improvement in 0.25µm process technology achieves gate delays for n-channel and p-channel transistors of 3.5 and 7.8 psec (CV/I) [8], respectively, which is half that of the previous 0.35µm technology [9]. Although transistor drive current is about the same as in the previous

technology, this gate delay improvement increases the current density in metal lines and vias for high performance microprocessors. Five metal layers are developed to provide low metal line/via resistance and good electromigration performance. Metal interconnect pitch and thickness are summarized in Table 4 along with those for the 0.35µm technology [8-9].

|         | 0.25um<br>Technology |                |            | 35um<br>hnology |

|---------|----------------------|----------------|------------|-----------------|

| Layer   | Pitch<br>(um)        | Thickness (um) | Pitch (um) | Thickness (um)  |

| Metal 1 | 0.64                 | 0.48           | 0.88       | 0.60            |

| Metal 2 | 0.93                 | 0.90           | 1.16       | 0.80            |

| Metal 3 | 0.93                 | 0.90           | 1.16       | 0.80            |

| Metal 4 | 1.60                 | 1.33           | 1.70       | 1.70            |

| Metal 5 | 2.56                 | 1.90           | N/A        | N/A             |

Table 4: Metal layer pitches and thickness

Without major architectural changes in metallization to improve electromigration resistance, the thickness of M2 and M3 lines (used for intermediate interconnect) was increased from 0.80µm to 0.90µm. The inter-level dielectric process was optimized to support aggressive metal aspect ratios. However, the M1 line (used for local interconnect) thickness was decreased from 0.60µm to 0.48µm for narrow pitch planarity improvement. M1 current density increases significantly as compared to the other layers, and effort has been focused on process improvement, electromigration design rule characterization and implementation.

The thin Ti shunt layer used in Ti/Al-Cu/Ti/TiN metal stack forms a TiAl $_3$  compound at the end of silicon processing. The quality and thickness uniformity of the shunt layer has been found to be key to M1 line electromigration resistance. In addition, the top TiN ARC process has also been optimized to become a reliable shunt layer. However, metal width and length dependence of electromigration performance was not considered in the previous  $0.35\mu m$  process technology. Therefore, during the  $0.25\mu m$  process development, attention was paid to characterization of the electromigration of narrow and short metal lines.

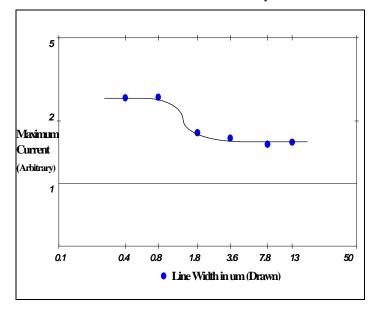

M1 electromigration structures with different metal width and length were designed in the SRAM test chip;

constant temperature and current density stresses were used in the characterization. Figure 9 shows M1 electromigration performance vs. line width. It is clear that minimum metal lines with 0.4 $\mu$ m drawn (preshrink) improves performance ~50% over the wide line structures, which are used for process monitoring. In microprocessors, the majority of M1 lines are used for local interconnect with minimum width for density improvement. Designers can use this narrow metal width electromigration advantage to support enhancement of transistor drive current density.

**Figure 9:** M1 electromigration performance vs. line width

It has been reported that short metal lines with tungsten plugs significantly improve electromigration due to vacancy back pressure effects [10]. Different stress current densities were applied to various metal length structures, and resistance changes vs. stress time were recorded to characterize the void formation. interesting to find that when metal line length is reduced to a certain value, void formation is saturated especially under relative low current density stress, indicating that electromigration depletion and back diffusion reach an equilibrium. The maximum percentage of line resistance increase is well below 30%, which is the electromigration failure criterion. Therefore, a short metal line electromigration design rule conservatively is implemented support short local transistor interconnect.

Electromigration occurs during unidirectional current stress but not during AC current stress. A design rule is developed for AC signal lines, based on a maximum allowable amount of resistive heating in the interconnects. Heat transfer through metal lines and inter-layer dielectric was simulated using a two-dimensional model. The design rule was derived based on a reasonable local temperature rise; and experimental data were taken on the test structures to calibrate the model. Electromigration requirements were built into the development of standard library cells, and design-rule checks were developed at the Function Unit Block (FUB) and Full Chip stages.

# **Gate Oxide Reliability**

Gate oxide integrity is another one of the reliability concerns for high-density, high-performance microprocessors. Transistor and capacitor leakage current will be degraded under voltage and temperature stresses leading to function or speed failures. To ensure the product Defect Per Million (DPM) and Failure In Time (FIT) rate meet Intel's reliability goals, a high-quality gate oxide process is required for the ultra thin oxide technology.

The 0.25µm process technology gate-delay improvement comes from both transistor architect and gate oxide thickness reduction from 60 nm to 42 nm. Power supply voltage was reduced from 2.8V to 2V to keep the oxide electric field unchanged while maintaining acceptable hot electron reliability and reducing power consumption in high performance microprocessors. Although the electrical field across the gate oxide increases slightly on 0.25µm process technology, thin gate oxide reliability in terms of initial gate leakage, latent defect, and intrinsic integrity was well characterized during technology development. Besides the appropriate surface clean prior to the gate oxide growth and poly silicon gate deposition to improve oxide quality, process charging damage elimination and antenna layout rules are also implemented to ensure a low product field failure rate due to gate oxide breakdown.

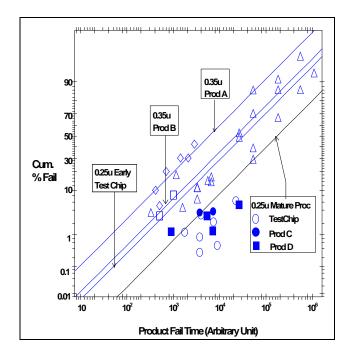

Breakdown Voltage of Gate (BVG), Constant/Ramp Current Density Stress (JT), Ig Gate Current Measurement, and Time Depend Dielectric Breakdown (TDDB) test methodologies were used to characterize process charging induced gate oxide damage [11]. High Voltage Extent Life Test (HVELT) was also used on the test chip and on products to calculate the field product failure rate. Figure 9 shows the HVELT Time-To-Fail (TTF) distributions of 0.35μm and 0.25μm Test Chip and products after normalizing to the same electrical field and temperature. Product A in the 0.35μm process technology has the highest gate oxide failure rate though it still meets Intel's reliability goal of less than 0.1% failures in 10 years of product life. Detailed fault

isolation and failure analysis unveiled gate oxide damage; and circuit layout analysis discovered a huge metal antenna ratio (to the gate area) was the culprit for oxide breakdown. The gate oxide failure rate of Product B without metal antenna violations is improved by 3.8X over Product A.

With this knowledge, the 0.25µm technology process charging induced gate oxide damage was extensively characterized on Inter-Layer-Dielectric (ILD) deposition/etching and metal etch processes. Appropriate test structures were designed in the Test Chip such that reliable metal antenna design rules could be derived. Reliability validation tools to check antenna layout rules were also developed to catch and fix any design rule violations before products are taped out.

Gate oxide failure rate in 0.25μm pre-mature process was measured on the Test Chip. The result is quite similar to that of the 0.35μm Product B shown in Figure 10. Subsequent processes resulted in a reduction in the product failure rate. TTF (without area normalization) distributions of the Test Chip, Product C, and Product D in mature 0.25μm technology are plotted in Figure 2. Taking a conservative approach, when data were fitted with a -1 sigma distribution as shown by the solid line in Figure 10, the 0.25μm product failure rate improves 7.2X over that of the 0.35μm product failure rate. This improvement has opened the way to additional reductions in gate-oxide thickness, improving process speed.

**Figure 10:** Comparison of 0.35µm and 0.25µm gate oxide breakdown TTF distributions

# **Aspects of Mechanical Stress**

The last reliability topic we discuss is modeling of mechanical stress effects. These effects are the result of large die sizes and the use of new and novel package technologies such as Intel's plastic-mounted flip-chip technologies. As both the die size and the number of back-end layers increase, mechanical interactions between the package and the silicon die, metallization, and device become concerns of both reliability and failures. We now describe the approach taken to both model and mitigate such failures.

There are two parts to mechanical stress: the intrinsic part  $(\sigma i)$  and the externally applied part  $(\sigma e)$ . The total stress is the sum of the two as shown in Eq(1).

#### $\sigma$ total = $\sigma$ intrinsic + $\sigma$ applied (1)

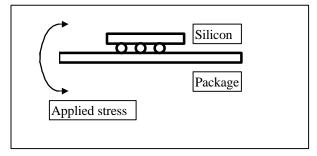

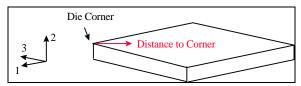

We have used finite element models to calculate the magnitude of the strains resulting from  $\sigma$  applied, the externally applied stress. The basis of this model is shown in Figure 11 where the die and the package are treated as two beams. (Note that the "fliped-chip" is being modeled in this figure). We use this dual-beam approach to estimate stresses in various parts of the final packaged component.

**Figure 11:** Externally applied stresses on silicon with the chip and package viewed as two independent beams

Using this kind of modeling, an informed choice can be made when selecting materials for various parts of the complete package. Materials are selected on the basis of compatible coefficients of thermal expansion, elastic moduli, and strength in order to maximize reliability performance.

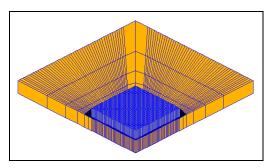

A second use of this model is to examine in greater detail some of the spatial stress relationships. In order to perform these calculations, we start by making a "3-D finite-element mesh" of the package die. An example of this is shown in Figure 12.

**Figure12a:** Global model showing a quarter-slice of a die (in gray) mounted on a plastic package (yellow)

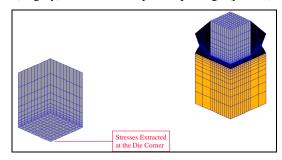

Figure 12b: Stress extracted at the die corner

Figures 12a and 12b show how global package models are meshed and how local stresses are determined. Figure 12a is the "global" model showing a quarter-slice of a die mounted on a plastic package. (Only the half plane is shown and the other half follows by symmetry. The mesh is provided courtesy of Drs. George Raiser and Nancy Fang, both at Intel.) When the material's properties (modulus, coefficient of expansion, etc.) are put in, the model will provide stress in various layers.

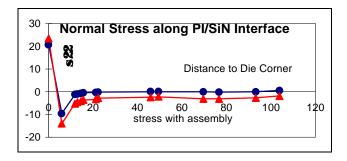

The global model in Figures 12a and 12b is then taken and put into a detailed die-level model. The die-level model is shown in Figure 13a.

Figure 13a: Stress components

**Figure 13b:** Result of calculations showing that the stresses are altered after assembly

The results of this analysis (Figure 13b) help us both in selecting materials as well as in defining the layout design rules to mitigate failures. These models allow detailed analysis of corner areas that are subject to the most stress.

We have also studied the effects of stress on transistors, and our results show that stress does not play any part in the degradation of transistor stability.

# **Discussion—Limits to Energy Scaling**

From Table 2 it may occur to the discerning reader that a reduction in the total power consumed microprocessors will lead to an enhancement in the lifetime of a device. In fact, Von Neuman stated that the process of manipulating 0s and 1s could be accomplished without the expenditure of entropy and hence energy. We refer to this as the vN computer. Using this as an absolute reference you may ask what "practical" power dissipation is possible. Both Keyes [13] and Meindl [12] have shown that the "ideal" switching process in an ersatz but "practical" quantum mechanical computer could switch with power as low as 10e-41 Joules per switching even. Real computers take much more energy—about 10 e-11 Joules. It can be seen from this that present day computers expend vastly more energy per switching event than the ersatz computer (in fact by a factor of e+31 in the example above).

It can therefore be argued that from a reliability scaling point of view, enhanced reliability could be achieved if the energy per switching event could be reduced. Simple scaling of voltage could continue to about ~10kT, but we may approach other materials' limits before ever reaching energy limits, Meindl [12]. However, significant effort has to be made to reduce the power consumption of future microprocessors, and this effort will also contribute to their extended reliability.

Before reaching the lowest possible operating voltage, it is likely that other limits like materials' limited RC delays will set in. This is likely to call for new materials with lower RC constants (such as, copper with low-k dielectrics), and these new materials will undoubtedly bring fresh reliability challenges. One may therefore expect to see both new combinations of materials and new reliability phenomena in the coming generations.

#### Conclusion

In this paper, we show that for Intel's 0.25µm process technology based products, electrostatic discharge protection of gates, electromigration in metal lines, gate oxide reliability, and mechanical reliability have been modeled, measured, studied, and characterized; and that our design methodology ensures that the quality of our products is equal to that of previous generations.

We note that the channel length, gate thickness, and voltage undergo a scaling process with operating voltage and are internally consistent with a "constant E-filed" scaling scheme. However, power, current, and size of the integrated and multi-functional microprocessors—and the stress effects on them when mounted in complex packages—are not scaling in a systematic manner. We believe that both these tendencies will constitute the challenges of the future.

### Acknowledgments

We acknowledge useful technical discussions with Neal Mielke and Paco Leon and leaders of the Protection, EM, and Stress working groups. We also thank our immediate Intel management for support and encouragement in writing this paper.

#### References

- Component Quality and Reliability, Intel Technical Publication, Literature Center, POB 7641, Mt. Prospect Il 60056-7641.

- G. Notermans, "On the Use of N-Well Resistors for Uniform Triggering of ESD Protection Elements," 1997 EOS/ESD Symposium Proceedings, pp. 221-229.

- 3. T.J. Maloney and S. Dabral, "Novel Clamp Circuits for IC Power Supply Protection," 1995 EOS/ESD Symposium Proceedings, pp. 1-12. Revised version published in IEEE Trans. on Components, Packaging, and Manufacturing Technology, Part C, 19, pp. 150-161, July 1996.

- R. Merrill and E. Issaq, "ESD Design Methodology," 1993 EOS/ESD Symposium Proceedings, pp. 223-237.

- E.R. Worley, et. al., "Sub-micron Chip ESD Protection Schemes Which Avoid Avalanching Junctions," 1995 EOS/ESD Symposium Proceedings, pp. 13-20.

- 6. T.J. Maloney and T.M. Eiles, "MOSFET-Based Power Supply Clamps for Electrostatic Discharge

- Protection of Integrated Circuits," US Patent application, filed 3/25/97.

- 7. T. Toyabe, et. al., "A Numerical Model of Avalanche Breakdown in MOSFETs," *IEEE Trans. Electron Devices, ED-25*, 825-832 (1978).

- 8. M. Bohr, et. al., "A High Performance 0.35μm Logic Technology for 3.3V and 2.5V Operation," 1994 Proceedings of the IEEE International Electron Devices Meeting, pp. 273-276.

- 9. M. Bohr, et. al., "A High Performance 0.25μm Logic Technology Optimized for 1.8V Operation," 1996 Proceedings of the IEEE International Electron Devices Meeting, pp. 847-850.

- 10. R. Filippi et al., *Journal Of Applied Physics*, 1995, pp. 3756 3768.

- 11. YH Lee, et al., *P2ID Technical Digest*, 1998, pp. 38 41.

- 12. J. D. Meindl "Low Power Microelectronics: Retrospect and Prospect" *Proceedings of IEEE v.83* (4), pp. 619-635, 1995.

- 13. R.W. Keyes "Physical Limits in Digital Electronics," *Proceedings IEEE v.63*, pp. 740-766. May 1975.

# **Authors' Biographies**

Krishna Seshan received a M.Sc in Low Temperature Physics from the University of Lancaster, UK, and a Ph.D. in Materials Science EE from the University of California at Berkeley in 1975. He is involved in aspects of mechanical stress management and the interaction of stress with all device levels. He works as a technical staff member in Intel's 0.25 μm Process Integration team. His email address is krishna.seshan@intel.com.

Timothy J. Maloney received degrees in physics from the Massachusetts Institute of Technology and Cornell University and ended with a Ph.D. (1976) in electrical engineering and postdoctoral studies at Cornell University. He was employed in semiconductor research at Varian Associates, Palo Alto, CA, from 1977 until he joined Intel in 1984. Since then, he has been concerned with integrated circuit ESD protection, CMOS latchup testing, fab process reliability, and design and testing of standard IC layouts. In 1994, he received the Intel Achievement Award for his patented ESD protection devices, which have achieved breakthrough ESD performance enhancements for a wide variety of Intel products. In 1996, he became a Principal Engineer at Intel. He is a Senior Member of the IEEE. His email address is timothy.j.maloney@intel.com.

Kenneth J. Wu received his B.S. (E.E.) from the National

Taiwan University in 1975, his M.S. (E.E.) from Northwestern University in 1978, and his Ph.D. (E.E.) from Princeton University in 1982. He joined Intel Corporation in 1982 working on process technology development in SRAM, Microprocessor, and Non-Volatile Memory technologies. He is interested in the areas of dielectric, gate charging, hot carrier, charge retention, electromigration, and assembly/package related reliability issues. Currently, he is Intel's 0.25μm Microprocessor Technology Reliability Program Manager. His email address is kenneth.j.wu@intel.com.

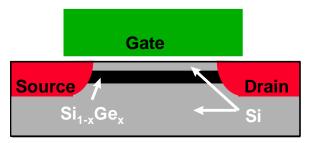

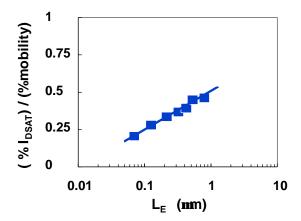

# MOS Scaling: Transistor Challenges for the 21st Century

Scott Thompson, Portland Technology Development, Intel Corp. Paul Packan, Technology Computer Aided Design, Intel Corp. Mark Bohr, Portland Technology Development, Intel Corp.

Index words: SDE, transistor, scaling

#### **Abstract**

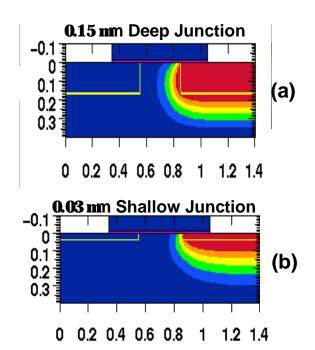

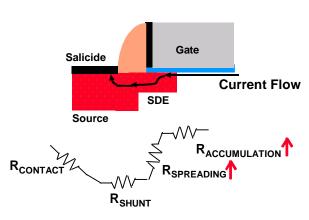

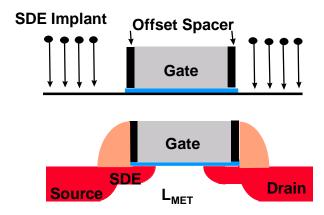

Conventional scaling of gate oxide thickness, source/drain extension (SDE), junction depths, and gate lengths have enabled MOS gate dimensions to be reduced from 10µm in the 1970's to a present day size of 0.1µm. To enable transistor scaling into the 21st century, new solutions such as high dielectric constant materials for gate insulation and shallow, ultra low resistivity junctions need to be developed. In this paper, for the first time, key scaling limits are quantified for MOS transistors (see Table 1). We show that traditional SiO<sub>2</sub> gate dielectrics will reach fundamental leakage limits, due to tunneling, for an effective electrical thickness below 2.3 nm. Experimental data and simulations are used to show that although conventional scaling of junction depths is still possible, increased resistance for junction depths below 30 nm results in performance degradation. Because of these limits, it will not be possible to further improve short channel effects. This will result in either unacceptable off-state leakage currents or strongly degraded device performance for gate lengths below 0.10µm. MOS transistor limits will be reached for 0.13µm process technologies in production during 2002. Because of these problems, new solutions will need to be developed for continued transistor scaling. We discuss some of the proposed solutions including high dielectric constant gate materials and alternate device architectures.

| FEATURE             | LIMIT                  | REASON                         |

|---------------------|------------------------|--------------------------------|

| Oxide Thickness     | 2.3 nm                 | Leakage (I <sub>GATE</sub> )   |

| Junction Depth      | 30 nm                  | Resistance (R <sub>SDE</sub> ) |

| Channel Doping      | V <sub>T</sub> =0.25 V | Leakage (I <sub>OFF</sub> )    |

| SDE Under Diffusion | 15 nm                  | Resistance (R <sub>INV</sub> ) |

| Channel Length      | 0.06μm                 | Leakage (I <sub>OFF</sub> )    |

| Gate Length         | 0.10μm                 | Leakage (I <sub>OFF</sub> )    |

**Table 1:** Fundamental scaling limits for conventional MOS devices

#### Introduction

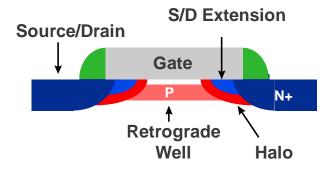

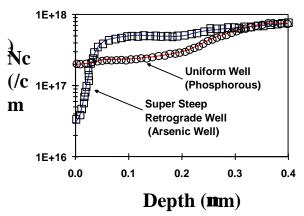

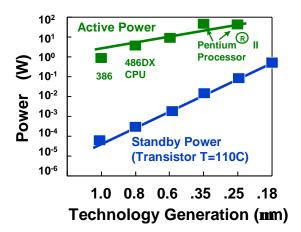

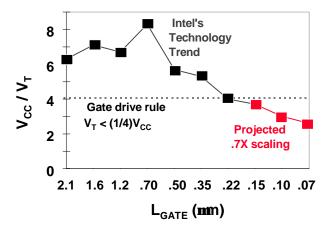

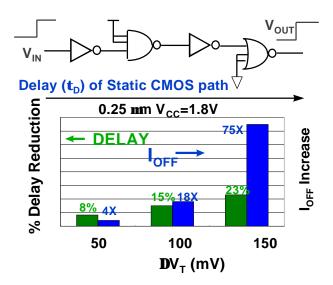

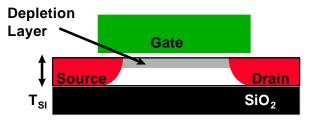

For more than 30 years, MOS device technologies have been improving at a dramatic rate [1,2]. A large part of the success of the MOS transistor is due to the fact that it can be scaled to increasingly smaller dimensions, which results in higher performance. The ability to improve performance consistently while decreasing power consumption has made CMOS architecture the dominant technology for integrated circuits. The scaling of the CMOS transistor has been the primary factor driving improvements microprocessor in performance. Transistor delay times have decreased by more than 30% per technology generation resulting in a doubling of microprocessor performance every two years. In order to maintain this rapid rate of improvement, aggressive engineering of the source/drain and well regions is required. In this paper, key methods for improving device performance are discussed. Creating shallow source/drain extension (SDE) profiles for improved short channel effects, the use of retrograde and halo well profiles to improve leakage characteristics, and the effect of scaling the gate oxide thickness are discussed in detail. Fundamental tradeoffs and scaling trends in engineering these effects are analyzed through experimental data and computer simulations. The impact of these trends associated with circuit requirements including power supply, threshold voltage, and off-state leakage on transistor design is also explored. We show that the scaling trends of the last ten years will be extremely difficult if not impossible to maintain unless new methods for device improvement are found. In addition to the conventional MOS transistor, several alternate device architectures are analyzed to understand the potential gains and tradeoffs associated with each device. The ability to overcome current physical technology limits such as gate oxide thickness and shallow junction formation as well as tradeoffs in circuit design will determine if MOS transistors can be scaled into the next century.

# **Oxide Scaling**

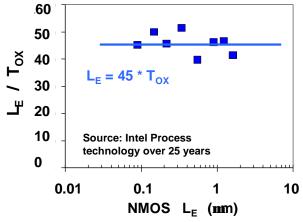

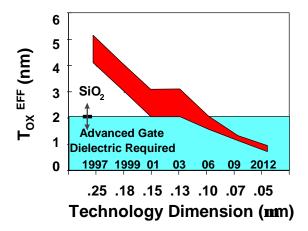

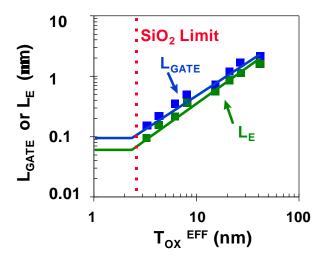

Gate oxide thickness scaling has been instrumental in controlling short channel effects as MOS gate dimensions have been reduced from 10µm to 0.1µm. Gate oxide thickness must be approximately linearly scaled with channel length to maintain the same amount of gate control over the channel to ensure good short channel behavior. Figure 1 plots the electrical channel length divided by gate oxide thickness for Intel's process technologies over the past 20 years. Each data point represents a process technology, developed approximately every three years, which was used to fabricate Intel's leading-edge microprocessors.

**Figure 1:** Channel length divided by gate oxide thickness versus channel length

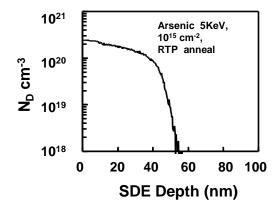

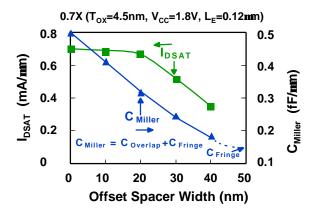

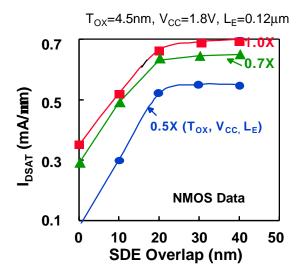

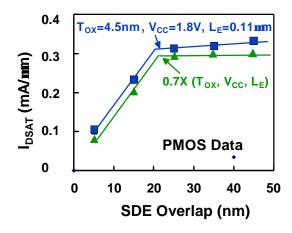

From Figure 1, a simple relationship between oxide thickness and the minimum channel length set by short channel effects is observed:

$$L_E = 45 * T_{OX}$$

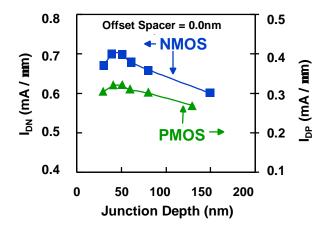

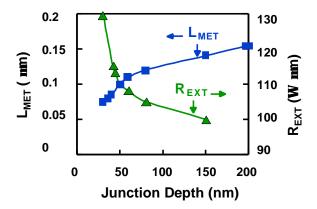

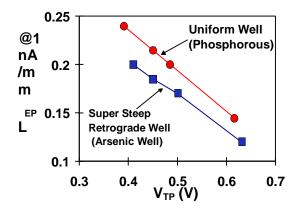

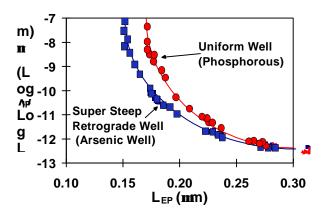

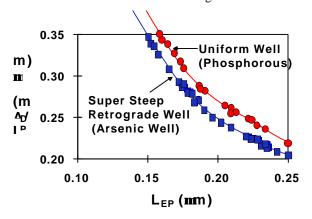

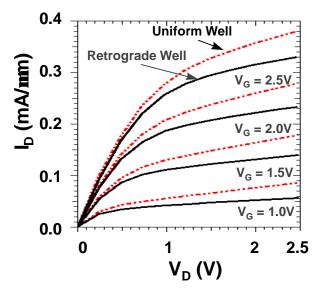

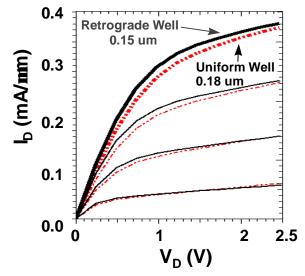

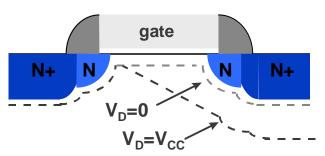

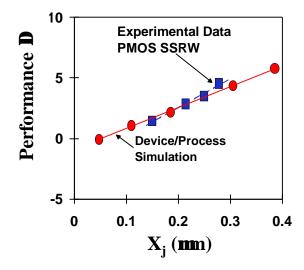

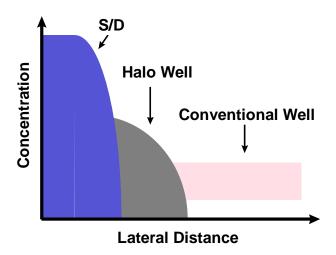

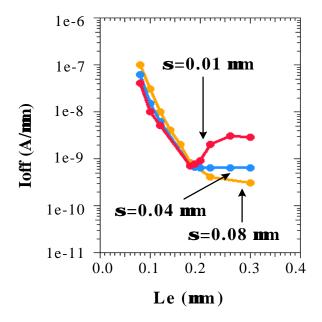

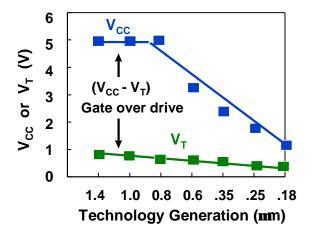

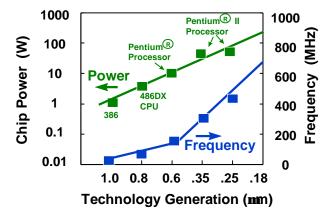

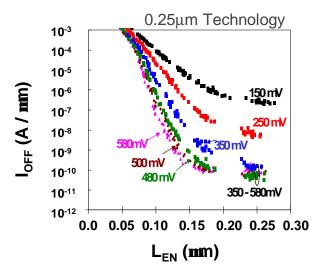

(Eq. 1)