PLL-less PHY IP complements the existing digital NAND Flash controller for a complete ASIC implementation of an ONFi compatible memory System-on-Chip.

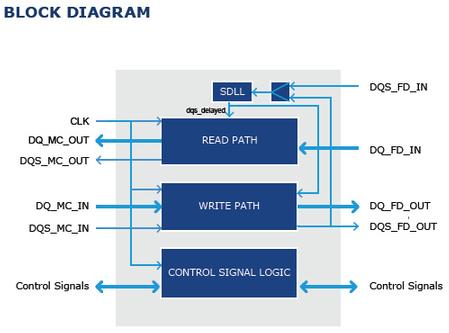

The implementation of an internal Synthesizable Delay Locked Loop (SDLL) relieves application designers from applying an external PLL and secures seamless integration of all components necessary for NAND Flash memory interconnection. Together with the Evatronix NAND Flash Memory Controller IP, the SDLL PHY IP forms an optimized, scalable system that will maximize the application performance while keeping silicon area and power consumption values at the lowest possible level.

“With the release of the SDLL NAND Flash PHY IP, we are confirming our focus on PHY IP announced last month through the release of the USB HSIC PHY,” said Wojciech Sakowski, Evatronix CEO. “In both cases we remove the integration burden off the designer’s shoulders and accelerate their time-to-market in these very innovative areas.”

"Simplifying the development of NAND flash applications for SoC designers is an important step forward as we aim to grow adoption of industry standards, like ONFi 2.x and the recently ratified ONFI 3.0," said Jim Cooke, ONFi Marketing Chair. "We appreciate the contribution from Evatronix to provide the necessary IP to support ONFI’s high-speed memories in the most demanding applications."

The joint implementation of Evatronix NAND Flash memory digital and PHY IP provides support for High-Speed memories and secures data transfer of up to 200 MT/s. Full utilization of all NAND Flash device source synchronous speed modes is available through the implementation of the SDLL component that provides appropriate delay for the DQS signal in the data path.

Evatronix SDLL-NANDFLASH-PHY Availability

The Evatronix SDLL-NANDFLASH-PHY logic macro is available now on the LFoundry 150nm process with the possibility to port it to different technology nodes on request.